# PROCESADOR ÓPTICO CON MATRIZ DE ENTRADA BINARIA CON 256 PUNTOS DE RESOLUCIÓN

## Víctor Ramos, Eduardo Gómez y Moisés Alencastre Laboratorio del Centro de Investigación, Universidad La Salle

Benjamin Franklin 47, Col. Hipódromo-Condesa, México DF 06170, email: vramos@ci.ulsa.mx

#### RESUMEN

En este trabajo se presenta el diseño de una tarjeta electrónica de control para la etapa de entrada de patrones bidimensionales a una computadora óptica utilizando una PC como interfaz de comunicación. La resolución de la entrada es de 256 puntos arreglados en una matriz de 16 \* 16 emisores de luz (LED's).

#### ABSTRACT

The design of an electronic control board for the input stage of an optical computer is presented. This system uses a PC as a communication interface. The maximum resolution for the input pattern is 256 point fixed in a 16\*16 matrix of Light Emission Diodes.

## INTRODUCCIÓN

Actualmente la computación digital no es la única alternativa para el procesamiento de información y existe un esfuerzo importante en el desarrollo de elementos de tipo analógico que en un futuro desplacen o compitan con la teoría digital.

Una de las alternativas en las cuales poco a poco se han tenido desarrollos importantes es la Computación Óptica. Esta herramienta surge como una alternativa al procesamiento masivo de información, ya que como sugiere su nombre, principalmente trabaja con la formación de imágenes bidimensionales, es decir, con la generación, propagación y detección de ondas de luz, que permiten la realización de un gran número de operaciones ópticas que se interconectan en paralelo.

Estrictamente las operaciones se realizan a la velocidad de la luz, sin embargo, aun no se puede desarrollar una Computadora Optica (C.O.) 100% óptica, es decir que todavía se requiere de la electrónica para realizar el manejo de la información de entrada y salida por medio de interfases.

Es en este punto donde se ha desarrollado un sistema electrónico para el manejo de patrones de entrada a la C.O. que permita manejar información binaria desde una computadora personal, de una forma accesible para el usuario.

Gomez-Mayol (1) propusieron un sistema de entrada de datos que constaba de 64 nodos o emisores de luz (matriz de 8x8) que almacenaba la información en 64 Flip-Flop's que representaban 16 circuitos integrados solo para almacenar el patrón de entrada, mas los circutos de control y comunicacion con la P.C. El prototipo propuesto en este artículo pretende mejorar las características de la versión anterior, ya que maneja 256 nodos (matriz 16x16) de entrada que

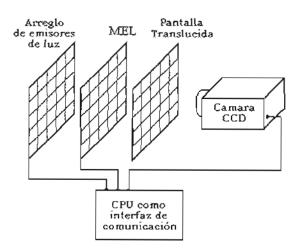

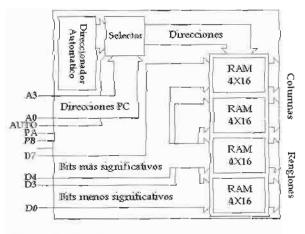

Fig. 1 Arquitectura básica de un procesador óptico.

son almacenados en 4 memorias RAM de 4x16 lo que representa solo 4 circuitos integrados.

Los desarrollos en Compútación Óptica, pueden tomar dos caminos: el de desarrollar nuevos materiales para procesamientos puramente ópticos, y el de desarrollar nuevas arquitecturas para eficientar los procesos. Este ultimo es el caso de la C.O. reportada en el presente artículo

#### ARQUITECTURA

La arquitectura de una computadora óptica (2), consta básicamente de tres etapas, la entrada, el proceso o programa y la salida (Figura 1). La entrada está constituida por un arreglo matricial de emisores puntuales de luz (nodos), como pueden ser una matriz de LED's o un arreglo de lentes con iluminación controlada independientemente.

El proceso lo conforma un Modulador Espacial de Luz (MEL), que puede ser un acetato o una pantalla de cristal líquido, teniendo la función de modular la información luminosa proveniente del arreglo de emisores de luz.

La salida o analizador, no es mas que la proyección de sombras, generadas por la entrada a través del MEL, en pantalla translúcida, de donde puede ser capturada por medio de una cámara de CCD.

#### PROCESAMIENTO ÓPTICO

Para Ilevar a cabo la correlación óptica, es necesario aplicar una técnica para la codificación con base en los patrones de sombras generados por el proceso óptico, esta técnica se conoce como *Shadow-Casting* (3).

Se requiere tener una configuración geométrica tal que las sombras de resultado se

$$d = \frac{sb}{s - b}$$

Ec. 1

$$l_1 + l_2 = \frac{sl_1}{s - b}$$

(b < s) Ec. 2

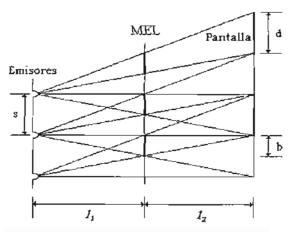

Fig. 2 Configuración geométrica para Shadow-Casting.

traslapen en fracciones exactas, como lo muestra la Figura 2.

Las condiciones para cumplir con ésta configuración geométrica son:

cuando 2b y 2d son el tamaño de las celdas en el objeto de entrada y las imágenes proyectadas en las direcciones vertical y horizontal respectivamente;  $l_1$  es la distancia que existe del plano de emisores de luz hasta el modulador espacial y  $l_2$  es la distancia entre el modulador espacial y la pantalla; s es el espaciamiento que existe entre las lentes del plano de emisores tanto vertical como horizontalmente.

Suponiendo que la matriz de entrada se encuentra formada por cuatro emisores de luz en un arreglo matricial de 2x2 el diagrama de sombra de la celda *ij* obtenida por la iluminación de los cuatro emisores se traslaparán en la pantalla defasados uno de otro por la mitad del tamaño de la celda proyectada tanto vertical como horizontalmente.

En el área central del diagrama de sombras, donde las cuatro proyecciones de la celda ij se traslapan, la intensidad está evaluada por Ec. 3, donde  $\alpha$ ,  $\beta$ ,  $\gamma$  y  $\delta$  son valores que representan la intensidad de los emisores de luz en porcentaje. " \* " Representa una operación lógica AND y " + " representa una operación lógica OR.

$$p_{y} = \alpha \bullet (a_{y} \bullet b_{y}) + \beta \bullet (a_{y} \bullet b_{y}) + \gamma \bullet (a_{y} \bullet b_{y}) + \delta \bullet (a_{y} \bullet b_{y})$$

Ec.3

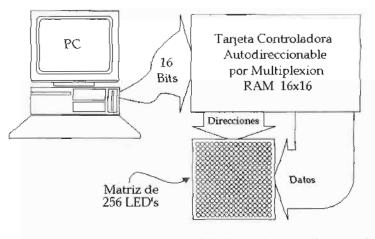

Figura. 3. Proceso de control de los patrones de entrada.

#### SISTEMA DE CONTROL

La entrada al procesador óptico, está constituida por tres bloques funcionales principales. El primer bloque es una matriz de LED's de 16x16.

El segundo bloque es una tarjeta controladora diseñada especialmente para manejar la matriz..

El tercer bloque consta de dos puertos paralelos en una PC que se conectan a la tarjeta controladora como se muestra en la Figura 3.

La tarjeta se controla por medio de un programa especial, que permite la generación de patrones de una forma muy sencilla para posteriormente mandar la información al puerto para que sea desplegado el patrón en la matriz de entrada.

### MATRIZ DE LED's

Para el diseño y fabricación de la etapa de entrada al procesador, se utilizaron LED's de la marca DEL, modelo DEL-LUG31dD color verde difuso, con las siguientes características eléctricas:

Tabla 1. Características eléctricas del LED

| Intensidad Luminosa (mCd)<br>I <sub>F</sub> = 10 mA |      | @1 <sub>F</sub><br>(mA) |  |

|-----------------------------------------------------|------|-------------------------|--|

| min                                                 | max  |                         |  |

| 5.0                                                 | 12.5 | 10                      |  |

La matriz de LED's, que es la que permite introducir patrones al procesador óptico, está formada por un arreglo de 16X16 LED's separados

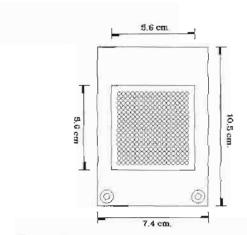

Fig. 4. Dimensiones de la matriz de entrada.

entre sus centros por una distancia de 5 mm. La matriz se encuentra ensamblada sobre una tarjeta de circuito impreso como se muestra en la Figura 4

Para facilitar el control de la matriz de LED's y reducir el número de circuitos integrados para su control, el circuito de control se reduce a un arreglo para la multiplexión de 16 líneas de datos que forman los renglones con 16 líneas de dirección que forman las columnas. La red se forma conectando los cátodos de los LED's en renglones y conectando los ánodos en columnas, de tal forma que se pueda controlar independientemente cada uno de los 256 LED's que forman la matriz, con tan solo 32 líneas de información.

## TARJETA CONTROLADORA PARA LA MATRIZ DE LED'S

La tarjeta controladora para la matriz de LED's (figura 5), consta de un bloque de memoria RAM, que es cargado por medio de una PC. Consta además de un circuito especial encargado de autodireccionar al bloque de memoria RAM, de tal forma que se libere el puerto de la PC para que ésta pueda atender otras tareas, mientras el patrón es mantenido en la matriz para realizar una determinada operación.

La tarjeta controladora utiliza 16 bits para la entrada de información, de los cuales, 8 bits están destinados para datos, 4 bits para las direcciones de memoria RAM y 4 bits para señales de control. En la tabla 2 se muestran las funciones de las terminales de datos y de control de la tarjeta.

Los 8 bits de datos cargan al bloque de memoria en dos pasos; en el primer paso los 8 bits cargan la parte baja de la memoria RAM habilitando la terminal de control PB y en un segundo paso cargan la parte alta habilitando la terminal de control PA, para tener en total 16 bits de información del patrón por cada localidad de memoria.

Figura 5. Diagrama de bloques de la tarjeta controladora.

Tabla 2. Funciones de las terminales de la tarjeta controladora.

| TERMINAL | FUNCIÓN                                  |

|----------|------------------------------------------|

| A0-A3    | Canal de Direcciones                     |

| AUTO     | Habilità el modo de autodireccionamiento |

| PA       | Carga la parte alta de la memoria        |

| P8       | Carga la parte baja de la memoria        |

| D0-D7    | Canal de Datos                           |

Los 4 bits de direcciones permiten indicarle al bloque de memoria la localidad en la cual se va a almacenar el dato de 16 bits, cuando la tarjeta esta siendo cargada y direccionada directamente por la computadora PC. Cuando la tarjeta esta en modo de autodireccionamiento, una vez cargado el patrón en el bloque de memoria, los 4 bits de direcciones son decodificados para activar una de 16 columnas a la vez.

### Programación de la Tarjeta

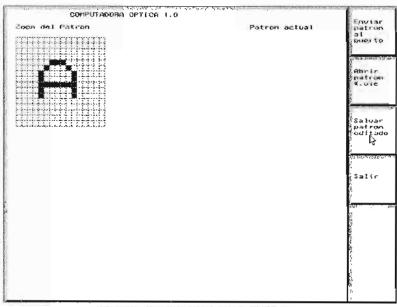

Se desarrolló un programa en *Turbo Pascal* 7.0, para el diseño de patrones de 256 elementos arreglados en una matriz de 16X16. El programa brinda la facilidad de editar un patrón gráficamente por medio del "mouse" de la PC.

| 16 16             |

|-------------------|

| 00000000000000000 |

| 00000000000000000 |

| 00000000000000000 |

| 00000000000000000 |

| 0000000111000000  |

| 0000001000100000  |

| 000001000010000   |

| 0000010000010000  |

| 0000011111110000  |

| 0000010000010000  |

| 0000010000010000  |

| 00000000000000000 |

| 00000000000000000 |

| 00000000000000000 |

| 00000000000000000 |

| 00000000000000000 |

Figura 6, Archivo de texto de un patron

El patrón es almacenado en un archivo de texto en el que primero se indica las dimensiones de la matriz y posteriormente los 256 datos de la matriz expresados en 1's y en 0's, como se muestra en la figura 6. Los 1's representan los LED's que se tienen que encender y los 0's los que se tienen que mantener apagados.

El programa, para comunicarse con la tarjeta controladora, direcciona dos puertos paralelos unidireccionales: el puerto \$378 y el puerto \$278, como se muestra en la tabla 3.

Donde A3-A0 son las direcciones para controlar la tarjeta, Au permite el autodireccionamiento de la tarjeta, Pa carga la parte alta de la matriz, Pb carga la parte baja de la matriz, H habilita la tarjeta

y D7-D0 son los datos. Los bits de control se encuentran en la parte baja del puerto \$378 y son activos con un nivel bajo

Tabla 3.Configuración de los puertos paralelos \$378 y \$278.

|    |    |    | \$3 | 78 |    |    |    |

|----|----|----|-----|----|----|----|----|

| B7 | B6 | B5 | B4  | B3 | B2 | B1 | BO |

| A3 | A2 | A1 | A0  | Au | Pa | Pb | H  |

|    |    |    | \$2 | 78 |    |    |    |

| B7 | B6 | B5 | B4  | B3 | B2 | 81 | B0 |

| D7 | D6 | D5 | D4  | D3 | D2 | D1 | D0 |

El programa se denomina "Computadora Óptica" en su versión 1.0. Tiene un ambiente gráfico dividido en dos zonas (Figura 7). La primera es un área de gráficos y la segunda es una barra de funciones. En la parte izquierda de la zona de gráficos hay una retícula de 256 celdas para la edición de patrones, en la derecha se puede visualizar el patrón actual en pixeles.

La barra de funciones consta de cuatro botones:

El primero de ellos tiene la función de mandar el patrón que se encuentra en la retícula de edición al puerto de la PC, para ser desplegado en la matriz de LED's.

El segundo botón tiene la función de abrir un archivo que contenga un patrón ya existente para su edición o despliegue en la matriz.

El tercer botón tiene la función de guardar los cambios hechos a los patrones en un archivo.

El cuarto y último botón se utiliza para salir del programa.

### RESULTADOS

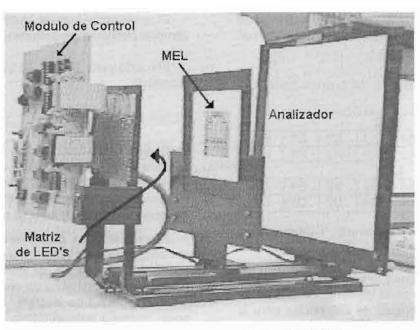

La Computadora Óptica en su última versión se muestra en la figura 8, en la que se puede apreciar la tarjeta controladora, la matriz de LED's, el modulador espacial de luz, y el analizador, todo montado sobre un riel para su ajuste.

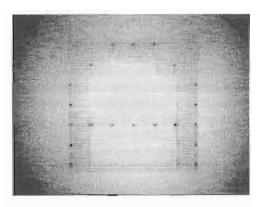

Se repitieron los experimentos realizados con anterioridad por Gómez-Mayol (1) así como por Ramos-Gómez (4), de los cuales solo se presentan los resultados de una red neuronal artificial (R.N.A.) de Hopfield (5) (Figura 9), como memoria autoasociativa e una entrada "A" con un patrón aprendido "A". Es decir, la R.N.A. implantada en la C.O. asocia dos patrones. Si el patrón a la entrada es igual al contenido en el MEL, la red lo reconoce y lo reconstruye. A medida que disminuye el parecido entre ambos patrones, la reconstrucción pierde intensidad hasta que ya no puede considerarse como reconstrucción. También se presentan los resultados para una red neuronal BAM (6) (Figura 10), como memoria heteroasociativa unidireccional de la entrada "A" con el patrón a sociado "Y". Es decir, asociamos dos patrones distintos. Cuando se

Figura 7. Archivo para edición.

Figura 8. Esquema de la Computadora óptica

Figura 9. Ejemplo de procesamiento óptico: Hopfield.

Figura 10. Ejemplo de procesamiento óptico: BAM.

coloca en la entrada una "A", la salida sera una "Y". Si secoloca una "Y" a la entrada la salida no reconstruye nada.

### CONCLUSIONES

La matriz de LED's permite aumentar la resolución de los patrones de entrada un 400% gracias a los 256 puntos que maneja, a diferencia de la versión anterior propuesta por Gómez-Mayol [1], que solo permitía manejar 64 puntos de resolución.

Por otra parte, el circuito de control para la matriz de LED's, que cuenta con un bloque de memoria RAM de 16 localidades por 4 bits, que representa solo 4 circuitos integrados, permite con ayuda del circuito de autodireccionamiento, mantener un patrón en la matriz sin tener la necesidad de mantener ocupado el puerto de la computadora. Substituyendo 64 Flip-Flop's de la primera versión, que representaban 16 circuitos integrados solo para almacenar el patrón de entrada,

La arquitectura del circuito, diseñada para la multiplexión de datos, permite reducir el número de componentes para realizar la función de desplegado del patrón, así como reducir el número de cables que conectan a la matriz con la tarjeta.

## REFERENCIAS

- 1. Mayol, W. & Gómez E., Desarrollo de una computadora optoelectrónica para el reconocimiento de patrones por técnicas neurocomputacionales. *Revista del Centro de Investigación*, Universidad la Salle, Vol. 1, No. 1, junio de 1993.

- Francis T.S. Yu & Suganda Jutamulia, Optical Signal Processing, Computing and Neural Networks, Wiley-Intercience, 1992.

- Ichioka Y. & Tanida J., Optical parallel logic gates using a Shadow-Casting technique, Systems for optical digital computing, IEEE, Vol. 72, No. 7, 1984.

- E. Gómez-Ramírez, V. Ramos-Viterbo, M. Alencastre-Miranda, A. Flores-Méndez, A. Sánchez-de-Tagle, Implementation of a cellular neural network over an optical computer. Fourth IEEE International Workshop of Cellular Neural Networks and its Applications. Seville, Spain, June 24-26 1996.

- Hopfield J., Neurons with graded response have collective computational properties like those of two-state neurons. *Proc. Natl. Acad. Sci.* USA, 81:3088-3092, Mayo 1984.

- Kosko B., Adaptive bidirectional associative memories, Applied Optics, 26(23):4947-4960, diciembre 1987.